# MOSTEK MICROCOMPUTER SYSTEMS DATA BOOK

# MICROCOMPUTER SYSTEMS DATA BOOK

Copyright © 1979 Mostek Corporation (All rights reserved)

Trade Marks Registered ®

Mostek reserves the right to make changes in specifications at any time and without notice. The information furnished by Mostek in this publication is believed to be accurate and reliable. However, no responsibility is assumed by Mostek for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patent rights of Mostek.

The "PRELIMINARY" designation on a Mostek data sheet indicates that the product is not characterized. The specifications are subject to change, are based on design goals or preliminary part evaluation, and are not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Mostek. Mostek reserves the right to make changes in specifications at any time and without notice.

PRINTED IN ENGLAND — SEPTEMBER 1979

Publication Number MK 79781

# MICROCOMPUTER SYSTEMS DATA BOOK

Part I

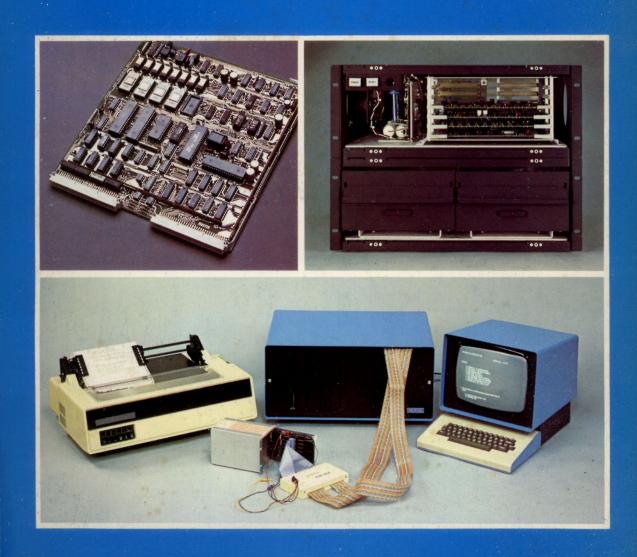

MD (Micro Design) Series

Stand-alone and expandable

OEM Microcomputer Boards

Part II

SD (System Design) Series

Double Eurocard OEM Microcomputers

Part III

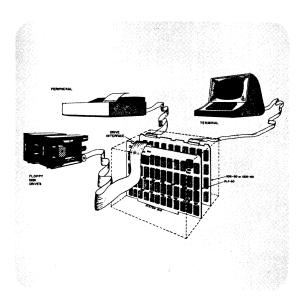

SYS-80 FT Floppy-disk based

Development System

Software

(See detailed index page 7.)

#### MOSTEK 1969-1979 TEN YEARS OF TECHNOLOGY LEADERSHIP

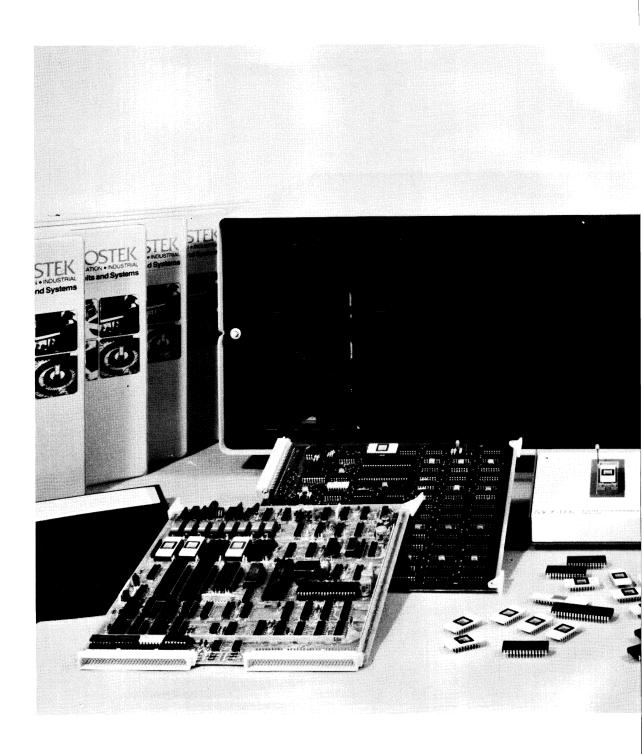

MOSTEK TECHNOLOGY. Technology links the past, present and future of Mostek. Innovations in both circuit and system design, and wafer processing have accounted for our rapid growth and for the strong acceptance of Mostek as a technology leader.

The proven process technology in the semiconductor industry is N-Channel silicon-gate MOS. Mostek is recognised as an important innovator in this process because of the continuing development of new techniques and enhancements which allow significant performance breakthroughs in our products. Competing technologies have not yet been able to approach either the performance or producibility of N-Channel MOS. Therefore, it appears that NMOS silicon-gate will continue to lead industry developments for several years to come.

MICROCOMPUTER COMPONENTS. Mostek's microcomputer products cover the full spectrum of microprocessor applications worldwide.

MOSTEK'S **Z80** is the most powerful 8-bit microcomputer available. It is software compatible with the 8080A yet has some significant system advantages — an increased instruction set, reduced dynamic memory interfacing costs, reduced I/O costs and reduced support circuitry costs.

MOSTEK'S 3870 FAMILY of single-chip microcomputers allow system flexibility and expansion while retaining the design and economic advantages of single-chip construction. Software compatible with the F8, Mostek's 3870 family is the answer to a wide range of low-cost microcomputer applications. MICROCOMPUTER SYSTEMS. Mostek's microcomputer line is supported by a wide array of development aids. These include software development boards that may be used as software development aids or as stand-alone microcomputers. Add-on memory boards, application interface modules, and emulators assist in system design, debugging and field testing. Now Mostek brings this experience to the Original Equipment Manufacturer.

Mostek's microcomputer line includes Mostek's MD Series™ of OEM microcomputer boards. The MD Series features both stand-alone boards (designated MD) and expandable boards (designated MDX) that are STD-Z80 BUS compatible. These powerful Z80-based boards are simple and economical to use.

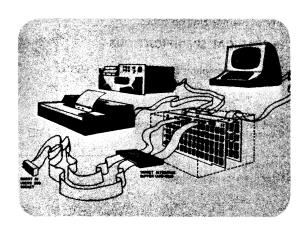

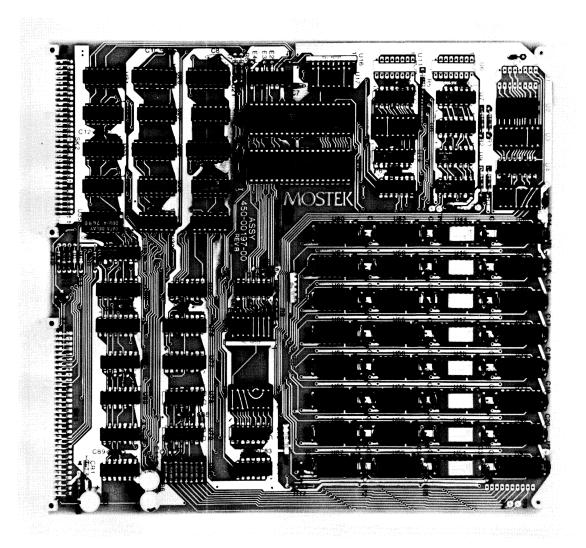

The System Design Series (SD Series<sup>™</sup>) of OEM microcomputer boards offers powerful features and versatility to the OEM. Utilizing the Mostek Z80 and Mostek's industry-standard memories, the SD Series enables the user to construct high-performance, memory-intensive systems for a wide range of applications.

Also included in the SD Series is a broad line of peripherals, software and development system support to speed and ease the design process. Mostek's floppy disk development system is built using the same cards shown here; this means your application can be prototyped on the system and later transferred to your own custom environment without software integration problems. Also, our AIM-80 application interface module and DDT-80 debug ROM will plug into any SD or MD System for quick testing of system hardware or software.

The products in this book are only the beginning of a full family of OEM products. New and innovative products are in design that will give further flexibility to the system designer.

### MOSTEK MICROCOMPUTER SYSTEM DATA BOOK

### **INDEX**

| INTRODUCTION                                              | 5                |

|-----------------------------------------------------------|------------------|

| MICRO DESIGN SERIES                                       | 9                |

| PRODUCT SPECIFICATIONS                                    |                  |

| Z80 Single Board Computer (MD-SBC1)                       | . 12             |

| MICRO DESIGN SERIES — EXPANDABLE                          |                  |

| PRODUCT SPECIFICATIONS                                    |                  |

| Central Processor Module (MDX-CPU1)                       | . 14             |

| Dynamic Ram Module (MDX-DRAM)                             | . 16             |

| EPROM/UART Module (MDX-EPROM/UART)                        | . 18             |

| Programmable Input/Output Unit (MDX-PIO)                  | 20               |

| Serial Input/Output Module (MDX-SIO)                      | 23               |

| Z80 Debug Module (MDX-DEBUG)                              | 26               |

| Z80 Debug Module (MDX-DEBUG)                              | 21               |

| Z80 Single Step Module (MDX-SST)                          | 22               |

| Universal Memory Card (MDX-UMC)                           | . აა             |

| EPROM Module (MDX-EPROM)                                  | . 35             |

| Static RAM Module (MDX-SRAM)                              | .3/              |

| Analog to Digital Conversion Module (MDX-A/D)             | . 39             |

| ORDERING INFORMATION                                      | . 41             |

| Prototyping Package (MDX-PROTO)                           | . 43             |

| MD Series New Products                                    | . 48             |

| MD Series Accessories (MD-ACC)                            | . 49             |

| APPLICATION NOTE: STD-BUS DESCRIPTIONN AND SPECIFICATIONS | . 53             |

| SYSTEM DESIGN SERIES (DOUBLE EUROCARD BOARDS)             | . 61             |

| PRODUCT SPECIFICATIONS                                    |                  |

| Software Development Board (SDB-80E)                      | . 63             |

| Single Board Microcomputer (OEM-80E)                      | 65               |

| EXPANSION BOARDS AND PRODUCTS                             |                  |

| Random Access Memory Board (RAM-80E)                      | 67               |

| Flexible Disk Drive Controller (FLP-80E)                  | 71               |

| Video Display Interface (VDI-S/P)                         | 7/               |

| Video Display Interface (VDI-5/P)                         | . / <del>4</del> |

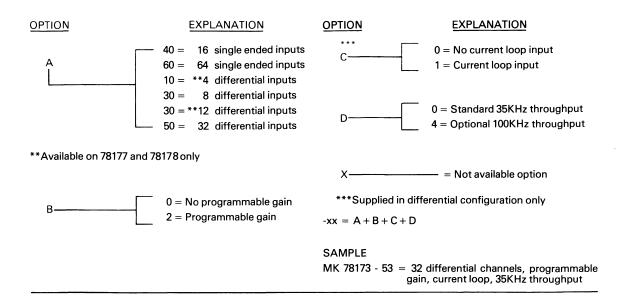

| Analog/Digital Converter (A/D-80E)                        | . //             |

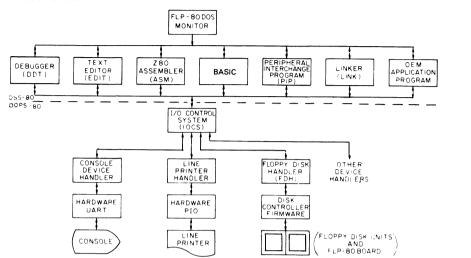

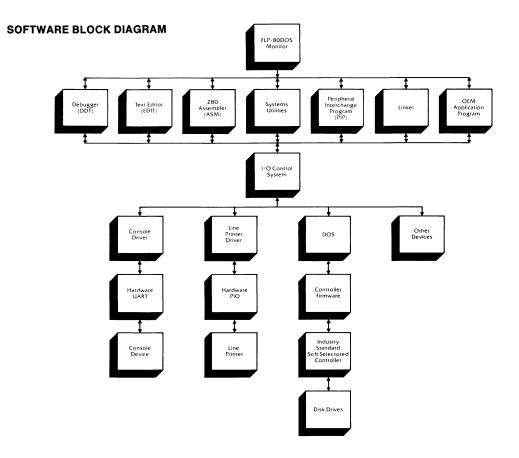

| Flexible Disk Operating System (FLP-80DOS)                | . გა             |

| Operating System (DDT-80)                                 | . 87             |

| SD SERIES COMING PRODUCTS                                 | . 89             |

| SD SERIES ACCESSORIES                                     | . 90             |

| MEMORY MAPPING PROMS FOR OEM 80                           |                  |

| ORDERING INFORMATION                                      | . 92             |

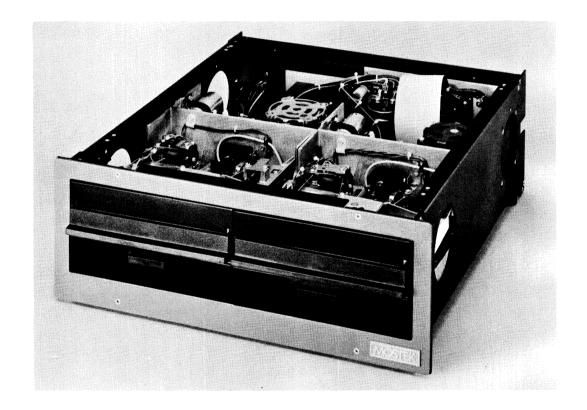

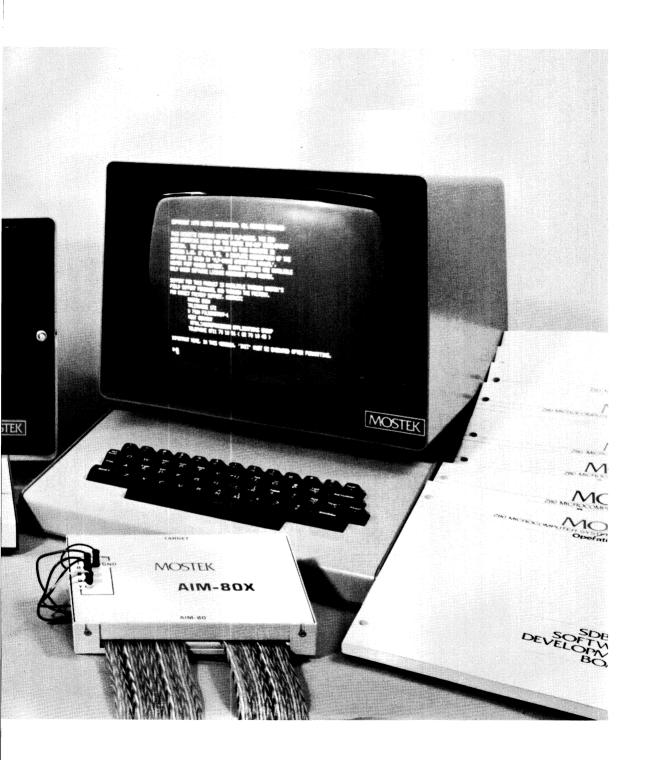

| DISK-BASED DEVELOPMENT SYSTEM AND MICROCOMPUTER           | . 95             |

| Microcomputer Development System (SYS-80FT)               | . 97             |

| SOFTWARE                                                  |                  |

| Z80 Macro Assembler (MACRO-80)                            | 105              |

| 3870/F8 Macro Assembler (MACRO-70)                        | 106              |

| Fortran IV Compiler                                       | 107              |

| Basic Interpreter                                         | 109              |

| Pascal                                                    | 113              |

| Micro Cobol                                               | 115              |

| ACCESSORIES AND DEVELOPMENT AIDS                          |                  |

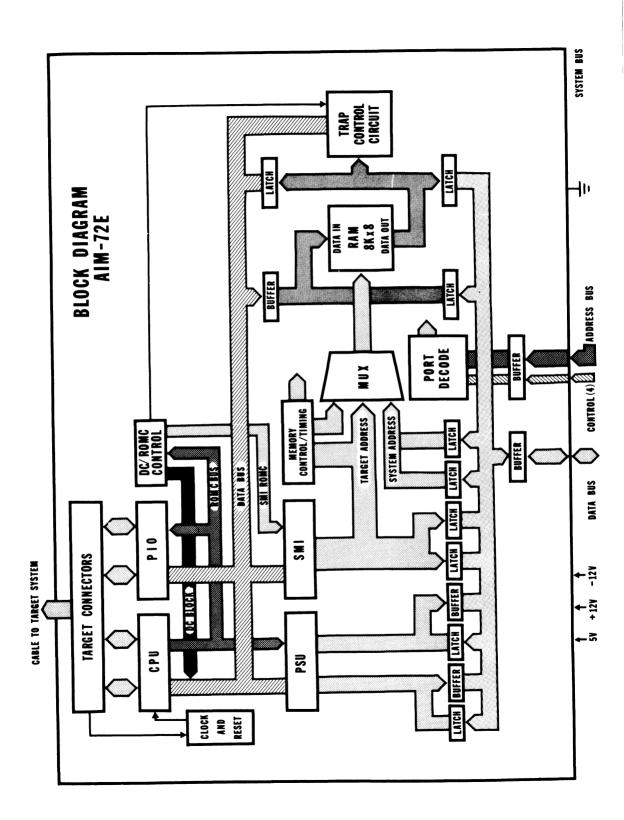

| Z80 Application Interface Module (AIM-80E)                | 117              |

| 3870 Application Interface Module (AIM-32E)               | 121              |

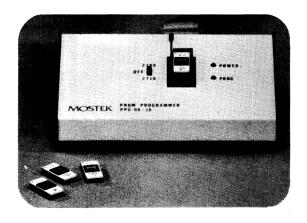

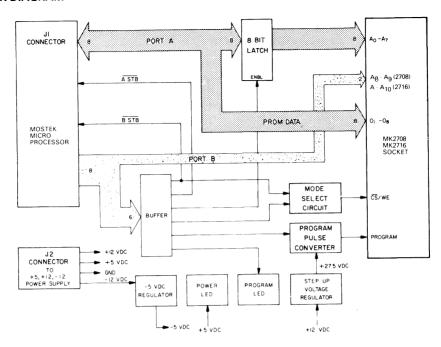

| PROM Programmer (PPG 8/16)                                | 125              |

| Line Printer                                              | 127              |

| ORDERING INFORMATION                                      | 121              |

| Software Agreement Form                                   | 133              |

| MOSTEK ADDRESSES IN EUROPE                                | 126              |

| INIO91EN ADDRESSES IN EUROPE                              | 100              |

# **MD** Series

### MOSTEK'S MD (MICRO DESIGN) SERIES Z80 MICROCOMPUTERS

#### **GENERAL DESCRIPTION**

In many OEM applications, such as process control, test equipment, industrial automation, energy management systems, etc..., the existing Single Board Microcomputers are insufficiently modular for the system design requirements.

Having recognised this need for a more cost effective approach, Mostek introduces now the MD Series of OEM Microcomputer modules.

To the design engineer, the Mostek MD Series provides Z80 power, well designed OEM boards, sophisticated software and extensive field support at an attractive price.

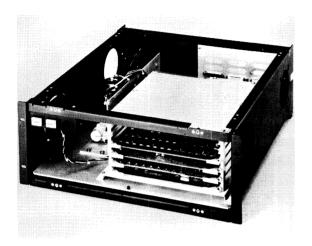

Each module operates from a Standard (STD) position independent bus, this STD BUS concept (developed jointly by Prolog and Mostek and rapidly gaining wide acceptance) uses a motherboard interconnect system.

The MD Series modules are thus fully expandable and can be organised in unrestricted combinations (any card works in any slot) to form a particularly cost effective microcomputer system, closely matching the application requirements.

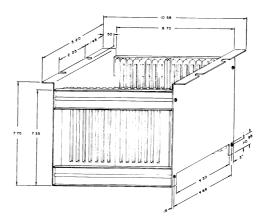

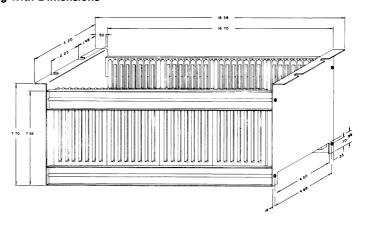

The MD Series comprises the following bus expandable modules (all in either 2.5 or 4.0 MHz versions) on  $114 \times 165$  mm  $(4.5 \times 6.5$  in.) cards:

MDX-CPU1 — Z80 CPU, 4K x 8 PROM.

256 x 8 RAM

MDX-DRAM - 8K, 16K or 32K x 8 add-on

dynamic RAM module

MDX-EPROM/UART— 10K x 8 universal PROM plus

UART add-on module

MDX-PIO - Fully buffered parallel I/O

controller

MDX-SIO — Multiprotocol asynchronous

or synchronous Serial I/O

interface

MDX-DEBUG — 10K bytes of Firmware

(DDT-80 ASMB-80) with Edit, Debug and Assemble capability to generate and Debug STD BUS programs

MDX-SST — Single step Debug module

MDX-UMC — Universal Memory Card

MDX-EPROM — EPROM Memory Extension

MDX-SRAM — 4K, 8K or 16K x 8 add-on

static RAM Module

MDX-A/D — 8 bit A/D Converter module

The MD Series also includes a fully functional, stand-alone microcomputer MD-SBC 1 on a single 114 x 165 mm (4.5 x 6.5 in) board.

Additional modules are being designed by Mostek to be made available shortly, see page 41.

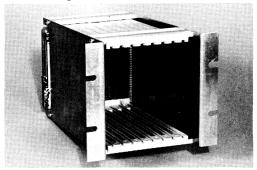

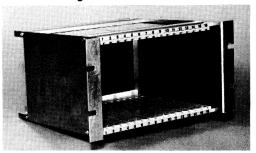

Of particular interest to the OEM design engineer is the Mostek MDX-PROTO comprising the CPU, DRAM and Debug modules together with the 8-slot card cage, STD bus motherboard and all accessories to form a ready to use prototyping kit.

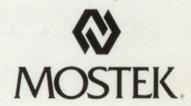

### MD SERIES SYSTEMS CONCEPT

# **Z80 Single Board Computer (MD-SBC1)**

#### **FEATURES**

| Z80 Microprocessor                    |

|---------------------------------------|

| 2K byte RAM capacity with 1K included |

| Sockets for 8K bytes 2716 EPROM       |

| Crystal Clock - 2.5 MHz               |

| Three TTL buffered 8-bit OUTPUT ports |

| Two TTL buffered 8-bit INPUT ports    |

| Two Interrupt Inputs                  |

| Single +5 volt power supply           |

#### DESCRIPTION

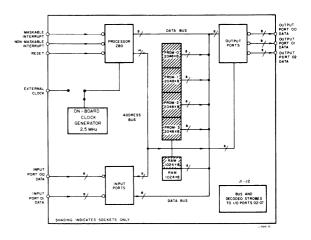

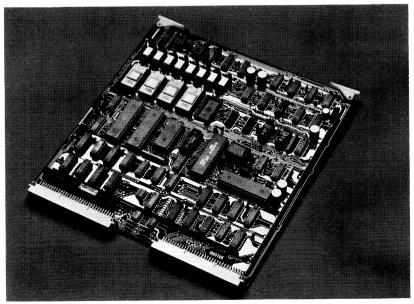

The MD-SBC1 is a complete Z80 based microcomputer on  $4\frac{1}{2}$  in. by  $6\frac{1}{2}$  in. circuit module. All I/O is fully TTL buffered and is brought to a 56 pin edge connector.

The smaller card size and the single power supply makes the MD-SBC1 easier to package and easier to use than most other modules. While the module size is small no compromises have been made in computing power due to increasing MOS-LSI densities and the use of the Z80 microcomputer. The 40 buffered TTL I/O lines and the 8K bytes of EPROM provide the capability to solve many control problems encountered by the OEM microcomputer user. The expandable MD Series (MDX) has the same form factor allowing easy expansion to a multi-board system with increased capability.

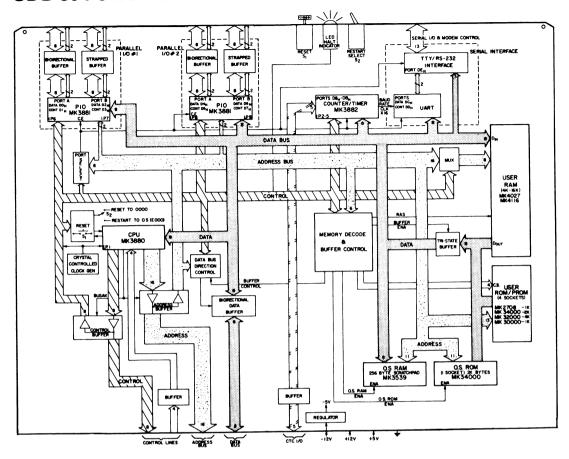

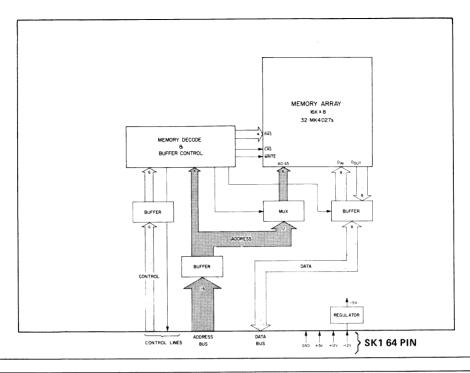

Figure 1 is a block diagram of the MD-SBC1. The basic module comes with 1K bytes of RAM expandable to 2K bytes by the addition of two 2114 type RAMs. Four 2716 sockets are provided for up to 8K bytes of EPROM, and are decoded in 2K blocks starting at address zero. The output ports are 74LS244 latches which are brought to the card cage connector. The input ports are 74LS240 Octal Buffers with 4.7K OHM pull-up resistors on the inputs. These input lines are also brought to the edge connector. The Z80-CPU is driven by a crystal clock at 2.5MHz (400nsec T-State).

Both the NMI and INT interrupt inputs to the Z80-CPU are terminated with 4.7K Ohm pull ups and brought to the card edge connector. An external clock can be used by changing strapping options on the board. Power on reset circuitry is included on the CPU's RESET input. Provision is made to expand the I/O capability through the use of on-board connectors.

### MD-SBC1 BLOCK DIAGRAM Figure 1

#### **ELECTRICAL SPECIFICATIONS**

#### **WORD SIZE**

INSTRUCTION 8, 16, 24 or 32 bits DATA 8 bits

#### **CYCLE TIME**

T-STATE = 400nSec, fastest instruction is 1.6 microsecond

#### **MEMORY ADDRESSING**

| EPROM<br>NUMBER |   | HEX<br>Address |

|-----------------|---|----------------|

| 0               |   | 0000-07FF      |

| 1               |   | 0800-0FFF      |

| 2               |   | 1000-17FF      |

| 3               | ļ | 1800-1FFF      |

| -               |   |                |

|                 |   |                |

| RAM<br>NUMBER | HEX<br>ADDRESS |

|---------------|----------------|

| STANDARD      | 2000-23FF      |

| OPTIONAL      | 2400-27FF      |

#### **MEMORY CAPACITY**

#### POWER SUPPLY REQUIREMENTS

8 K bytes of 2716 memory (none included)

2 K bytes of 2114 memory (1K bytes included)

+5 volts  $\pm 5\%$  at 1.2A max (fully loaded) (100mA per RAM, 100mA per EPROM)

#### MEMORY SPEED REQUIRED

| Memory | Access Time | Cycle Time |

|--------|-------------|------------|

|        | Required    | Required   |

| 2716*  | 450nSec     | 450nSec    |

| 2114   | 450nSec     | 450nSec    |

**OPERATING TEMPERATURE RANGE**

$0 \,^{\circ}\text{C}$  to  $+50 \,^{\circ}\text{C}$

#### MECHANICAL SPECIFICATIONS

#### I/O ADDRESSING AND CAPACITY

| PORT TYPE | HEX<br>Address | DATA CAPACITY |

|-----------|----------------|---------------|

| Input     | 00 and 01      | 16 lines      |

| Output    | 00, 01, 02     | 24 lines      |

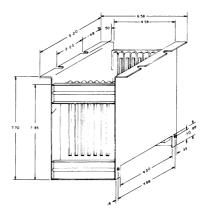

**CARD DIMENSIONS**

4.5 in. (11.43cm) high by 6.50 in. (16.51cm) long 048 in. (1.22cm) maximum profile thickness 0.062 in. (0.16cm) printed circuit board thickness

#### **INTERRUPTS**

Two active low: NMI and NT. See Z80-CPU (MK 3880) Technical Manual for a full description of Z80 interrupts.

#### CONNECTORS

| FUNCTION       | CONFIGURATION        | MATING<br>CONNECTOR                                                            |

|----------------|----------------------|--------------------------------------------------------------------------------|

| Paralleled I/O | 56 pin (28 position) | Printed Circuit<br>VIKING VH-<br>28/1 CK5                                      |

|                | 0.125 in centers     | Wire Wrap<br>VIKING 3VH-<br>28/1 CMD 1<br>Solder Lug<br>VIKING VH-<br>28/1 CL5 |

#### I/O INTERFACES

Inputs - One 74LS load plus a 4.7K Ohm pull up resistor Outputs -  $I_{OH} = 15$ mA at  $V_{OH} = 2.4$  volts  $I_{OI} = 12$ mA at  $V_{OL} = 0.4$  volts

#### SYSTEM CLOCK

|         | MIN    | MAX    |

|---------|--------|--------|

| MD-SBC1 | 250KHz | 2.5MHz |

#### ORDERING INFORMATION

| DESIGNATOR              | DESCRIPTION                                                                               | PART NO. |

|-------------------------|-------------------------------------------------------------------------------------------|----------|

| MD-SBC1                 | Complete Z80 Single Board Computer with Operation Manual less EPROMs and mating connector | MK77851  |

|                         | MD-SBC1 Operation Manual only                                                             | MK79609  |

| MDX-PROTO<br>Data Sheet | MD Series prototyping package                                                             | MK79605  |

| SYS-80F<br>Data Sheet   | Disk based development system                                                             | MK78575  |

| AIM-80E<br>Data Sheet   | Z80 In-Circuit Emulation Module                                                           | MK78571  |

<sup>\*</sup> Single 5 volt type required

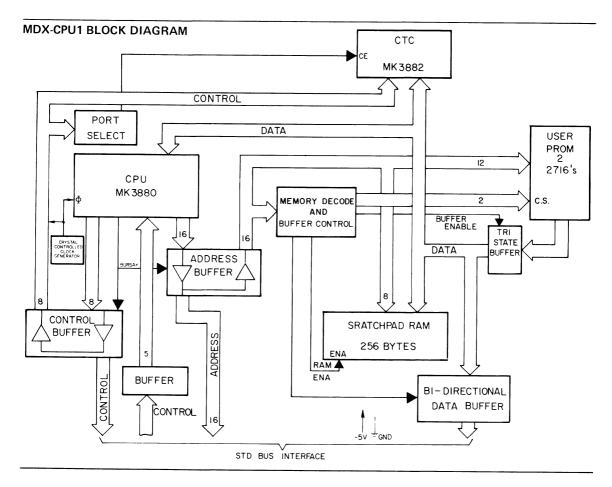

# **Z80 Central Processor Module (MDX-CPU1)**

#### **FEATURES**

|   | Z80 CPU                                              |

|---|------------------------------------------------------|

|   | 4K x 8 EPROM (2-1716's)                              |

|   | 256 x 8 Static RAM (compatible with DDT-80 debugger) |

|   | Flexible Memory decoding for EPROM and RAM           |

|   | A80-CTC with four timer channels                     |

|   | Restart to 0000H or E000H                            |

|   | Debug compatible for single step in DDT-80           |

|   | 4MHz version available                               |

|   | +5V only                                             |

|   | Fully buffered signals for system expandability      |

| П | STD BUSTM compatible                                 |

#### DESCRIPTION

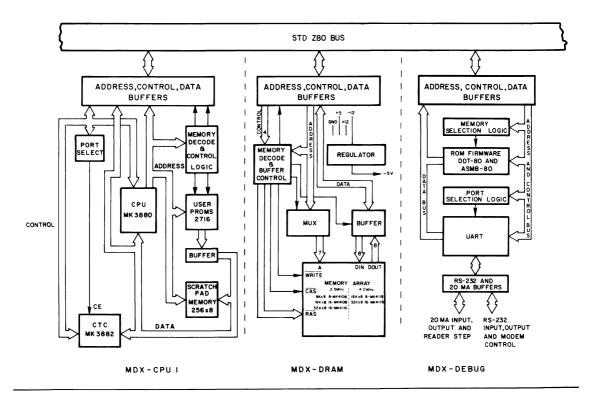

The MOSTEK MDX-CPU1 is the heart of an MD Series Z80 system. Based on the powerful Z80 micro-processor, the MDX-CPU1 can be used with great versatility in an OEM microcomputer system application. This is done simply by inserting custom ROM or EPROM memories into the sockets provided on the board and configuring them virtually anywhere within the Z80 memory map.

On-board memory is provided in the form of 4K of EPROM (2-2716's) and 256 bytes of scratchpad RAM as pictured in the block diagram. In addition, an MK3882 Counter Timer Circuit is included on the MDX-CPU1 to provide counting and timing functions for the Z80. Either 2716 EPROM can be located at any 2K boundary within any given 16K block in the Z80 memory map via a jumper arrangement.

The MDX-CPU1 can be used in conjunction with the MDX-DEBUG and MDX-DRAM modules to utilize DDT-80 and ASMB-80 in system development. This is accomplished by strapping the scratchpad RAM to reside at location FF00 so that it will act as the Operating System RAM for DDT-80.

The MDX-CPU1 is also available in 4MHz version (MDX-CPU1-4). In this version, one wait cycle is automatically inserted each time on-board memory is accessed by a read or write cycle. This is necessary to make the access times of the 2716 PROMs and the 3539 scratchpad RAM compatible with the MK3880-4 MHz Z80-CPU.

#### **WORD SIZE**

Instruction: 8, 16, 24, or 32 bits

Data: 8 bits

#### **CYCLE TIME**

Clock period or T state = 0.4 microsecond @ 2.5MHz 0.25 microsecond @ 4.00 MHz

Instructions require from 4 to 23 T states.

#### **MEMORY ADDRESSING**

On Board EPROM: jumper selectable for any 2K boundary within a 16K block of Z80 memory map.

On-Board RAM: FF00-FFFF.

#### **MEMORY CAPACITY**

On-Board EPROM - 4K bytes (sockets only).

On-Board RAM - 256 bytes.

Off-board Expansion - Up to 65,536 byte, with user-specified combinations of RAM, ROM, PROM.

#### MEMORY SPEED REQUIRED

| MEMORY | ACCESS TIME | CYCLETIME |

|--------|-------------|-----------|

| 2716*  | 450nS       | 450nS     |

<sup>\*</sup> Single 5 volt type required

#### I/O ADDRESSING On-Board Programmable Timer

| PORT          | MK 3882 |

|---------------|---------|

| ADDRESS (HEX) | CHANNEL |

| 7C            | 0       |

| 7D            | 1       |

| 7E            | 2       |

| 7H            | 3       |

#### I/O CAPACITY

Up to 252 port addresses can be decoded off board. Four port addresses are on board. 252 + 4 = 256 total I/O ports.

#### **INTERRUPTS**

Multi-level with three vectoring mode (Mode 0, 1, 2). Interrupt requests may originate from user-specified I/O or from the on-board MK3882 CTC.

## PARALLEL BUS INTERFACE - STD BUS COMPATIBLE

Inputs One 74LS load max

Bus Outputs  $^{I}OH = .3mA min at 2.4 volts$

IOL = 12 mA min at 0.4 volts

### SYSTEM CLOCK

MIN

MAX

MDX-CPU1

500 KHz

2,500 MHz

MDX-CPU-4

500 KHz

4,000 MHz

#### **POWER SUPPLY REQUIREMENTS**

5V  $\,\pm\,$  5% at 1.1A maximum

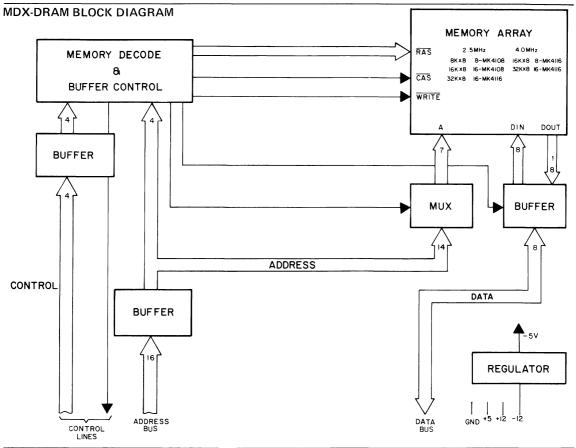

# Dynamic Ram Module (MDX-DRAM)

#### **FEATURES**

| Three memory sizes                      |

|-----------------------------------------|

| 8K×8 (MDX-DRAM8)                        |

| 16K x 8 (MDX-DRAM16)                    |

| 32K x 8 (MDX-DRAM32)                    |

| Selectable addressing on 4K boundaries. |

| 4MHz version available (MDX-DRAM-4)     |

| STD BUS compatible                      |

#### DESCRIPTION

The MDX-DRAM is designed to be a RAM memory expansion board for the MOSTEK MD SERIES of Z80 based microcomputers. It is available in three memory capacities: 8K bytes (MDX-DRAM8), 16K bytes (MDX-DRAM16), and 32K bytes (MDX-DRAM32). Additionally, the MDX-DRAM16 and the MDX-DRAM32 are available in a 4MHz version. Thus, the designer can choose from the various options to tailor his add-on dynamic RAM directly to his system requirements.

The MDX-DRAM8 is designed using MOSTEK'S MK4108 8, 192-bit dynamic RAM. The MDX-DRAM16 and MDX-DRAM32 utilize high-performance MK4116, 16,384-bit dynamic RAMs which allow 4MHz versions of these boards to be offered. No wait-state insertion circuitry is required on any of the RAM cards.

Address selection is provided on all MDX-DRAM cards for positioning the 8K, 16K, or 32K of memory to start on any 4K boundary.

# ELECTRICAL SPECIFICATIONS WORD SIZE

8 bits

#### **MEMORY SIZE**

MDX-DRAM8 - 8,192 bytes MDX-DRAM16 - 16,384 bytes MDX-DRAM32 - 32,768 bytes

#### **ACCESS TIMES**

| SYSTEM<br>CLOCK                        | MEMORY<br>ACCESS<br>TIMES | MEMORY<br>CYCLE<br>TIMES |

|----------------------------------------|---------------------------|--------------------------|

| MDX-DRAM 2.5 MHz<br>MDX-DRAM-4 4.0 MHz |                           | 465ns min.<br>325ns min. |

#### ADDRESS SELECTION

Selection of 8K, 16K, or 32K contiguous memory blocks to reside at any 4K boundary

## PARALLEL BUS INTERFACE-STD BUS COMPATIBLE

Inputs

One 74LS load max

**Bus Outputs**

IOH = -3mA min. at 2.4 volts

IOL= 12mA min. at 0.4 volts

#### SYSTEM CLOCK

|            | Min     | Max    |

|------------|---------|--------|

| MDX-DRAM   | 1.25MHz | 2.5MHz |

| MDX-DRAM-4 | 1.25MHz | 4.0MHz |

#### POWER SUPPLY REQUIREMENTS

$+5V~\pm5\%$  at 0.6A max.  $+12V~\pm5\%$  at 0.25A max.  $-12V~\pm5\%$  at 0.03A max.

#### **OPERATING TEMPERATURE**

$0\,^{\circ}\text{C}$  to  $50\,^{\circ}\text{C}$

## **EPROM/UART Module (MDX-EPROM/UART)**

# FEATURES 10K x 8 EPROM/ROM (2716's not included) Serial I/O channel RS - 232 and 20 mA interface

Reader step control for Teletypes Baud rate generator 110-19200 Baud

4MHz version available (MDX-EPROM/UART-4)

STD BUS compatible.

#### **DESCRIPTION**

The MDX-EPROM/UART is one of MOSTEK's complete line of STD BUS compatible Z80 microcomputer modules.

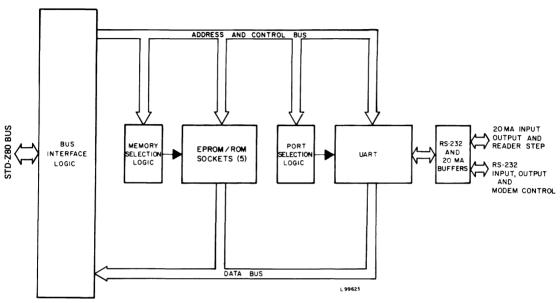

Designed as a universal EPROM add-on module for the STD BUS, the MDX-EPROM/UART provides the system designer with sockets to contain up to 10K x 8 of EPROM memory (5-2716's) as shown in the Block Diagram.

The EPROM memories can be positioned to start on any 2K boundary within a 16K block of memory via a strapping option provided on the MDX-EPROM/UART.

Included on-board the MDX-EPROM/UART is a fully buffered asynchronous I/O port with a Teletype reader step control. A full duplex UART is used to receive and transmit data at the serial port. Operation and UART options are under software control. Once the unit has been programmed, no further changes are necessary unless there is a modification of the serial data format. Features of the UART include:

Full duplex operation

Start bit verification

Data word size variable from 5 to 8 bits

One or two stop bit selection

Odd, even, or no parity option

One word buffering on both transmit and receive

The MDX-EPROM/UART is also available in a 4MHz version. Circuitry is provided to force one wait state each time on board EPROMs or the UART are accessed.

#### WORD SIZE

8 bits for PROM 5 to 8 bits for Serial I/O

#### **MEMORY ADDRESSING**

#### ROM/EPROM

2K blocks jumper selectable for any 2K boundary within a given 16K boundary of Z80 memory map.

#### MEMORY CAPACITY

10K bytes of 2716 memory. (2716's not included)

#### MEMORY SPEED REQUIRED

| MEMORY | ACCESS TIME | CYCLE TIME |

|--------|-------------|------------|

| 2716*  | 450ns       | 450ns      |

<sup>\*</sup> Single 5 Volt type required

#### I/O ADDRESSING

On-board Serial I/O Port Control Port DDH Data Port DCH

Modem and Reader Step Control DEH

#### I/O TRANSFER RATE

| X16 BAUD RATE CLOCK | BAUD RATE (Hz) |

|---------------------|----------------|

| 1760                | 110            |

| 4800                | 300            |

| 9600                | 600            |

| 19200               | 1200           |

| 38400               | 2400           |

| 76800               | 4800           |

| 153600              | 9600           |

| 317200              | 19200          |

#### SERIAL COMMUNICATIONS CHARACTERISTICS

Asynchronous

Full duplex operation

Start bit verification

Data word size variable from 5 to 8 bits.

One or two stop bits

Odd, even, or not parity

One word buffering on both transmit and receive.

#### SERIAL COMMUNICATIONS INTERFACE

BUFFERED FOR 20mA Current

SIGNAL Loop RS-232

Transmitted data Output Output Received data Input Input Reader Step Relay (RSR) Output (20mA)

Data Terminal Ready (DTR)

Request to Send (RTS)

Input

Carrier Detect (CDET)

Clear to Send (CTS)

Data Set Ready (SDR))

Input

Output

Output

Output

# PARALLEL BUS INTERFACE - STD BUS COMPATIBLE

#### SYSTEM CLOCK

Inputs Bus Outputs One 74LS Load Max

IOH = -3mA min at 2.4 Volts

IOL = 12mA min at 0.4 Volts

MDX-EPROM/UART MDX-EPROM/UART-4

MIN. 250 KHz 250 KHz MAX. 2.5 MHz 4.0 MHz

#### MDX-EPROM/UART BLOCK DIAGRAM

# Programmable Input/Output Unit (MDX-PIO)

### **FEATURES:** Four 8-bit I/O ports with 2 handshake lines per port All I/O lines fully buffered I/O lines TTL compatible with provision for termination resistor networks Jumper options for inverted or non-inverted handshake Two 8-bit ports capable of true bidirectional I/O Programmable In only, Out only, or Bidirectional Output data buffers selectable to provide inverted or non-inverted drive capability Interrupt driven programmability Address strap selectable STD BUS Compatible 4 MHz Option Fully buffered for MD Series expandability

#### DESCRIPTION

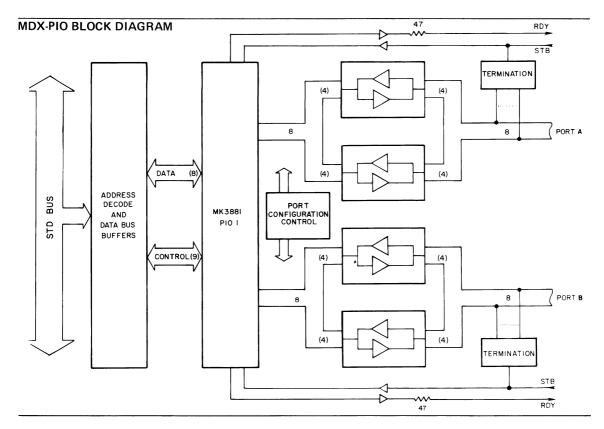

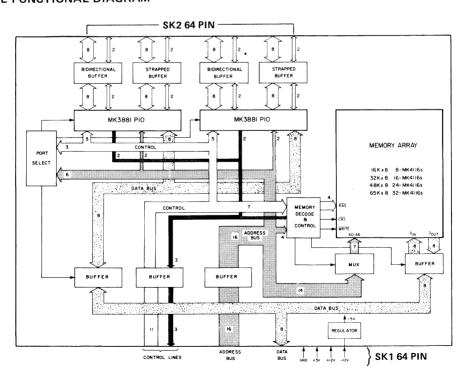

The parallel I/O controller (MDX-PIO) ia a highly versatile unit designed to provide a variety of methods for inputting and outputting data from the MD series microcomputer system. The system is designed around two Mostek MK3881 Z80-PIO parallel I/O controllers which give four independent 8-bit I/O ports with two handshake (data transfer) control lines per port. All I/O lines are buffered and have provisions for termination resistors on board. All port lines are brought to two 26 pin connectors; two ports per connector. Logically, each port pair A & B (connector) look similar (depending upon jumper options) to the on-card PIO devices.

Figure 1 illustrates in block diagram form the major functional elements of port pair A and B of Pl0 1. These elements can be defined as the resistor termination networks, data buffers, port configuration control, MK3881 Pl0, and address decode and data bus buffers. Input and output from the ports are provided through J1, a 26 pin connector. This connector provides data paths for the two ports and their respective handshake signals.

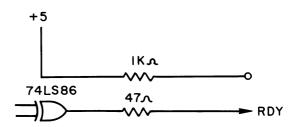

One 14-pin socket is provided per port for resistor dual inline packages so that terminations may be placed on the data lines. A parallel termination is provided for each 8-bit port data line plus the input strobe (STB) handshake line. The MDX-PIO is normally shipped with four 1K pullup terminators. In addition to the parallel termination resistors, the ready (RDY) handshake output line is series terminated with a 47  $\Omega$  resistor. This is used to damp and reduce reflections on the output line.

Port A and B data bus lines are buffered using quadruple non-inverting transceivers. The buffers can be configured using port configuration jumpers to provide fixed Input, fixed Output or Bidirectional (Port A only) signals. Further the transceivers are configured such that port direction can be selected in 4-bit sections. The transceivers are mounted in sockets so that they can be easily replaced with their complements in order to achieve a polarity change if desired.

The handshake lines are also fully buffered. The port configuration control provides jumper options to independently control the polarity or "sense" of each handshake line so as to further ease the interfacing between the MDX-PIO and peripheral devices.

The MK3881, PIO parallel I/O controller is the heart of the module. This circuit is a fully programmable two port device which provides a wide range of configuration options. Any one of four distinct modes of operation can be selected for a port. They are byte output, byte input, byte bidirectional (Port A only) and bit control mode. The PIO also automatically generates all handshaking signals in all the above modes.

The PIO permits total interrupt control so that full usage of the MDX-CPU interrupt capabilities can be utilized during I/O transfers. Also the PIO can be programmed to interrupt the CPU on the occurrence of a specified status condition in a specific peripheral device. The PIO circuit will provide vectored interrupts and maintain the daisy chain priority interrupt logic compatible with the STD RLIS

The address decoding, interface and bus management for the board are performed by the address decode and data bus circuit. Each MSX-PIO port has two addresses, one for control and one for Data. A total of eight addresses is utilized per board. These addresses are defined in the table below.

#### TABLE 1

|                 | PIO 1                                |                                      | PIO 2                                |                                      |

|-----------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

|                 | PORT A                               | PORT B                               | PORT A                               | PORT B                               |

| Data<br>Control | XX0 <sub>8</sub><br>XX1 <sub>8</sub> | XX2 <sub>8</sub><br>XX3 <sub>8</sub> | XX4 <sub>8</sub><br>XX5 <sub>8</sub> | XX6 <sub>8</sub><br>XX7 <sub>8</sub> |

The XX symbols stand for the upper 5 bits of the I/O channel address. These bits are jumper selectable on the MDX-PIO board in order to provide address selectable fully decoded ports.

The circuitry for the other two ports provided by PIO #2 is identical to PIO #1. The port configuration logic, buffers, termination and pin out on connector J-2 is duplicated for PIO #s. These two ports share the address decode and data bus buffer circuitry with PIO #1. The only differences are in the address decoding as given in the port address table, and PIO #2 is lower priority in the daisy chain interrupt structure.

#### **ELECTRICAL SPECIFICATIONS**

#### WORD SIZE:

Data: 8-bits

I/O Addressing: 8-bits

#### I/O ADDRESSING:

On-board programmable - See Table 1

#### I/O CAPACITY:

Parallel 4 8-bit ports. On board jumper, Port 1B and 2B only, (configurable in 4 bit bytes) as either In only, Out only or Bidirectional. Automatic handshake provided with each port.

#### **TERMINATORS:**

K ohm resistors on all I/O port lines.

### PARALLEL BUS INTERFACE-STD BUS COMPATIBLE

Inputs

One 74LS Load Max.

**Bus Outputs**

$I_{OH} = -3 \text{ mA min. at } 2.4 \text{ volts}$

$I_{OL} = 12$ mA min. at 0.4 volts

#### **INTERRUPTS**

#### SYSTEM CLOCK

Vectored interrupts generated. Interrupt vector programmable upon initialization. Daisy chained interrupt priority. Selected bit channels can be masked out under program control. MIN

MDX-PIO 250KHz

MDX-PIO-4 250KHz

MAX

KHz

2.5 MHz

KHz

4.0 MHz

#### I/O DRIVERS

The following line drivers and terminations are all compatible with the I/O driver sockets on the MDX-PIO.

| SIGNALS                         | TYPE     | OUTPUT                           | SINK CURRENT (mA) |

|---------------------------------|----------|----------------------------------|-------------------|

| Address, Data<br>Plus & Control | 74LS245  | NI<br>Tri-State<br>Bidirectional | 24                |

| I/O Ports 1A<br>and 2A          | *74LS244 | NI<br>Tri-State<br>Bidirectional | 24                |

|                                 | 74LS241  | l<br>Tri-State<br>Bidirectional  | 24                |

| I/O Ports 1B<br>and 2B          | *74LS243 | NI<br>Tri-State<br>Bidirectional | 24                |

|                                 | 74LS242  | NI<br>Tri-State<br>Bidirectional | 24                |

| Handshake:<br>RDY               | 7486     | I/NI (strap<br>selectable)       | 8                 |

Note: I = inverting

N.I. = non-inverting

These chips are normally supplied with the board. They may be exchanged with the other unit listed to provide the alternate signal polarity.

# Serial Input/Output Module (MDX-SIO)

#### **FEATURES**

| $\Box$ | Two independent full-duplex channels                          |

|--------|---------------------------------------------------------------|

|        | Independent programmable Baud rate clocks                     |

|        | Asynchronous data rates - 110 to 19.2K bits per second        |

|        | Receiver data registers quadruply buffered                    |

|        | Transmitter data registers double buffered                    |

|        | Asynchronous operation                                        |

|        | Binary synchronous operation                                  |

|        | HDLC or IBM SDLC operation                                    |

|        | Both CRC-16 and CRC-CCITT (-0 and -1) hardware implemented    |

|        | Modem control                                                 |

|        | Operates as DTE or DCE                                        |

|        | Serial input and output as either RS-232 or 20mA current loop |

|        | Current loop optically isolated                               |

|        | Current loop selectable for either active or passive mode     |

|        | Address programmable                                          |

|        | Compatible with STD BUS                                       |

#### DESCRIPTION

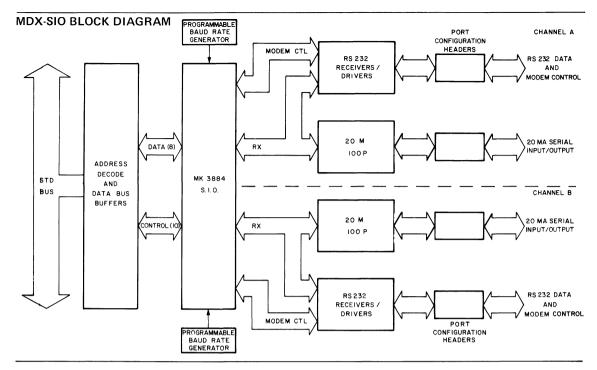

The Serial Input Output Module, MDX-SIO, is designed to be a multiprotocol asynchronous or synchronous I/O module for the STD BUS. The module is designed around the Mostek MK3884 Z80-SIO which provides two full duplex, serial data channels. Each channel has an independent programmable baud rate clock generator to increase module flexibility. Each channel is capable of handling asynchronous, synchronous, and synchronous bit oriented protocols such as IBM BiSync, IBM SDLC, HDLC and virtually any other serial protocol. It can generate CRC codes in any synchronous mode and can be programmed by the CPU for any traditional asynchronous format. The serial input and output data are fully buffered and is provided at the connector as either a 20mA current loop or RS-232-C levels. A modem control section is also provided for handshaking and status. The MDX-SIO module can be jumper configured as a data terminal (DTE) or as a modem (DCE) in order to facilitate a variety of interface configurations.

Figure 2 is a block diagram of the MDX-SIO module. It consists of five main elements. They are the channel configuration headers, line drivers and receivers, MK3884 Z80-SIO, programmable Baud rate generator, and address decode and data bus buffers. Input and output to the board is provided via two 26 pin connectors. One connector is dedicated for each channel. The configuration and pin out of each channel is identical.

Several features are available as options that are selected via the channel configuration header. The headers are used to select the orientation of the data communication interface and the mode of the 20mA current loop. The MDX-SIO can be selected to act as either a terminal or processor (Data Terminal Equipment DTE) or as the modem (Data Communications Equipment - DCE). The header allows reconfiguration of both data interchange and modem control signals. This allows increased flexibility necessary to link different hardware elements in OEM data link systems and networks. The module is shipped from the factory wired as a DTE interface.

The MDX-SIO has different selectable options for the 20mA current loop. The receiver and transmitter input and output lines can be reconfigured on the module to allow for reorientation of these signals. Also the receive and transmit circuits can be selected to function in either an active or passive mode. In the active mode, the MDX-SIO module provides the 20mA current source. In the passive mode, the module requires that the loop current be provided. The latter is the same mode as that of a Teletype.

An EIA and 20mA current loop interface circuit is used to provide the necessary level shifting and signal conditioning between the MK3884 Z80-SIO and the connector. These line drivers and receivers provide the correct electrical signal levels, slew rate and impedance for interfacing RS-232C and 20mA current loop peripherals. Additionally, optical isolation is provided for both transmit and receive circuits in the 20mA current loop mode.

The Mostek MK3884 Z80-SIO is the central element of this module. This device is a multifunction component designed to satisfy a wide variety of serial data communications requirements in microcomputer systems. Its basic role is this that of a serial to parallel, parallel to serial converter/controller but within that role it is configured by software programming so that its function can be optimized for a given serial data communications application. The MK3884 provides two independent full duplex channels; A and B. Each channel features the following:

- Asynchronous operation

- 5, 6, 7, or 8 bits/character

- 1, 1½ or 2 stop bits

- Even, odd or no parity

- x1, x16, x32 and x64 clock modes

- Break generation and detection

- Parity, Overrun and Framing error detection

- Binary Synchronous operation

- One or two Sync characters in separate registers

- Automatic Sync character insertion

- CRC generation and checking

- HDLC or IBM SDLC operation

- Automatic Zero insertion and deletion

- Automatic Flag Insertion

- Address field recognition

- I-Field residue handling

- Valid receive messages protected from overrun

- CRC generation and checking

The MK3884 also provides modem control inputs and outputs as well as daisy chain priority interrupt logic. Eight different interrupt vectors are generated by the SIO in response to various conditions affecting the data communications channel transmission and reception.

Address decoding, STD BUS interface and bus management for the module are performed by the Address Decode and Data Bus circuit. The MDX-SIO contains command registers that are programmed to select the desired operational mode. The addressing scheme is as follows:

| XXXXXX 00 | Channel A Data           |

|-----------|--------------------------|

| XXXXXX 01 | Channel B Data Command/  |

|           | Status                   |

| XXXXXX 10 | Channel A Command/Status |

| XXXXXX 11 | Channel B Command/Status |

The X indicates the binary code necessary to represent which of the 64 port address is selected.

Each channel has an individual programmable baud rate generator. The X1 multiplier on the Z80-SIO must be used in the synchronous mode. The X16, X32, or X64 Z80-SIO clock rate can be specified for the asynchronous mode. Table 1 indicates the possible baud rates available for both operation modes with the Z80-SIO Data Rate multipliers.

| Figure 1 |       |           |       |

|----------|-------|-----------|-------|

|          | BAUD  | RATE (HZ) |       |

| SYNCHRO  | NOUS  | ASYNCHRO  | NOUS  |

| X1       | X*16  | X32       | X64   |

| 800      | 50    | 25        | 12.5  |

| 1200     | 75    | 37.5      | 18.75 |

| 1760     | 110   | 55        | 27.50 |

| 2152     | 134.5 | 67.25     | 33.63 |

| 2400     | 150   | 75        | 37.50 |

| 4800     | 300   | 150       | 75    |

| 9600     | 600   | 300       | 150   |

| 19200    | 1200  | 600       | 300   |

| 28800    | 1800  | 900       | 450   |

| 32000    | 2000  | 1000      | 500   |

| 38400    | 2400  | 1200      | 600   |

| 57600    | 3600  | 1800      | 900   |

| 76800    | 4800  | 2400      | 1200  |

| 115200   | 7200  | 3600      | 1800  |

| 153600   | 9600  | 4800      | 2400  |

| 307200   | 19200 | 9600      | 4800  |

|          |       |           |       |

#### **ELECTRICAL SPECIFICATIONS**

#### **WORD SIZE**

Data: 8-bits

I/O addressing: 8-bits

#### I/O ADDRESSING

On board fully programmable

#### I/O CAPACITY

Serial - Two full duplex serial ports either synchronous of asynchronous. Special control registers and circuitry to permit implementation of SDLC, BiSync, Monosync, HDLC, and other formats can be programmed.

#### **SERIAL BAUD RATES**

See Table 1

#### **INTERRUPTS**

Generates vectored interrupts to 8 different locations corresponding to conditions within both channels. Interrupt vector location programmable. Daisy chained priority hardware interrupt circuitry.

#### SYSTEM CLOCK

|           | MIN    | MAX     |

|-----------|--------|---------|

| MDX-SIO   | 250KHz | 2.5 MHz |

| MDX-SIO-4 | 250KHz | 4.0 MHz |

#### **SERIAL COMMUNICATION INTERFACE**

Two identical ports

#### **BUFFERED FOR** 20mA CURRENT SIGNAL LOOP RS-232 Transmitted data Output Output Received data Input Input Data Terminal Input/Output Ready (DTR) Request to Send Input/Output (RTS) Clear to Send (CTS) Output/Input **Carrier Detect** Output/Input (CDET)

### PARALLEL BUS INTERFACE - STD COMPATIBLE

| Inputs      | One 74LS load max.                |

|-------------|-----------------------------------|

| Bus Outputs | $I_{OH} = 3mA min at 2.4 volts$   |

|             | $I_{OL} = 12$ mA min at 0.4 volts |

#### POWER SUPPLY REQUIREMENTS

+ 12 volts  $\pm$  5% at 72 mA max. -12 volts  $\pm$  5% at 46 mA max. + 5 volts  $\pm$  5% at 650 mA max.

# **Z80 Microcomputer Debug Module (MDX-DEBUG)**

| HAF                     | HARDWARE FEATURES                                                                                                                                                                                                                                                                                               |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                         | STD BUS compatible<br>4 MHz version available<br>Serial I/O Channel<br>10K bytes of ROM contain the following firmware                                                                                                                                                                                          |  |  |

| DEE                     | BUGGER FEATURES                                                                                                                                                                                                                                                                                                 |  |  |

|                         | Z80 Operating System with debug capability<br>Channelized I/O for versatility<br>I/O peripheral drivers supplied<br>ROM based                                                                                                                                                                                   |  |  |

| TEX                     | T EDITOR FEATURES                                                                                                                                                                                                                                                                                               |  |  |

|                         | Input and modification of ASCII Text<br>Line and character editing<br>Alternate command buffers for pseudo-macro com-<br>mand capability<br>ROM based                                                                                                                                                           |  |  |

| ASSEMBLER FEATURES      |                                                                                                                                                                                                                                                                                                                 |  |  |

|                         | Assembles all Z80 mnemonics Object output in industry standard hexadecimal format extended for Relocatable and Linkable Pro-                                                                                                                                                                                    |  |  |

|                         | grams Over fifteen pseudo-ops Two pass assembly ROM based                                                                                                                                                                                                                                                       |  |  |

| LINKING LOADER FEATURES |                                                                                                                                                                                                                                                                                                                 |  |  |

|                         | Loads into memory both relocatable and non-relocatable object output of the assembler Loads Relocatable modules anywhere in memory Automatically provides linkage of global symbols Automatically provides linkage of global symbols between object modules as they are loaded Prints system load map ROM based |  |  |

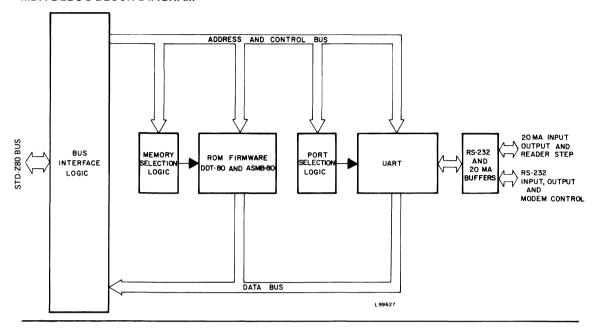

#### HARDWARE DESCRIPTION

The MDX-DEBUG Module has sockets for 10K bytes of masked ROM that are filled with a Z80 firmware package (DDT-80/ASMB-80). This module has a STD BUS interface and is available in both 2.5MHz and 4.0MHz versions. Included on-board is a fully buffered asynchronous I/O port capable of 110-19200 Baud Rates. Serial Data interfaces are available for 20mA current loop (with reader step control) and RS-232. The on-board Baud Rate Generator is selectable to all common Baud Rates from 110 to 19,200 Baud.

#### FIRMWARE DESCRIPTION

#### **DEBUGGER DESCRIPTION**

DDT-80 is the Operating System for the MDX-DEBUG Module. It resides in a 2K ROM (MK34000 series) resident on the MDX-DEBUG Module. It provides the necessary tools and techniques to operate the system, i.e., to efficiently and conveniently perform the tasks necessary to develop microcomputer software. DDT-80 is designed to support the user from initial design through production testing. It allows the user to display and update memory, registers, and ports, load and dump object files, set breakpoints, copy blocks of memory, and execute programs.

#### DDT-80 COMMAND SUMMARY

| M s    | - Display and/or update the contents of memory location s.                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------|

| M s, f | - Tabulate the contents to memory locations s through f.                                                                        |

| Ps     | <ul> <li>Display and/or update the content of I/O ports.</li> </ul>                                                             |

| Ds, f  | <ul> <li>Dump the contents of memory locations<br/>s through f in a format suitable to be read<br/>by the L command.</li> </ul> |

| L      | <ul> <li>Load, into memory, data which is in the appropriate format.</li> </ul>                                                 |

- Es Transfer control from DDT-80 to a user's program starting at location s.

- Perform 16 bit hexadecimal addition and/ or subtraction.

- C s, f, d

Copy the contents of memory locations s through f to another location in memory starting at location d.

#### MDX-DEBUG BLOCK DIAGRAM

Bs - Insert a breakpoint in the user's program (must be in RAM) at location s which transfers control back to DDT-80. This allows the user to intercept his program at a specific point (location s) and examine memory and CPU registers to determine if

memory and CPU registers to determine if this program is working correctly.

R - Display the contents of the user registers. The s, f, and d represent start, finish, and destination operands required for each command.

# MEMORY- PORT AND REGISTER COMMANDS (M, P, R)

The M, P, and R commands provide the means for displaying the contents of specified memory locations, port addresses, or CPU registers. The M and P commands sequentially access memory locations or ports and display their contents. The user has the option of updating the content of the memory location or port. (Note some ports are output only and their contents cannot be displayed). The M command also gives the user access to the CPU registers through an area in RAM called the Register Map (discussed in the Execute, Breakpoint section below).

The M and R commands are used to tabulate blocks of memory locations (M) or the CPU registers (R). The M command will accept two operands, the starting and ending address of the memory block to be tabulated. The R command will accept either no operand or one. If no operand is specified, the CPU registers will be displayed

without a heading. If an operand is specified then a heading which labels the registers contents will be displayed as well.

#### **EXECUTE AND BREAKPOINT (E, B)**

The E command is used to execute all programs, including aids such as the Assembler. The B command is used to set a breakpoint to exit from a program at some predetermined location for debugging purposes. At the instant of a breakpoint exit, the contents of all CPU register are saved in a designated area of MDX-DEBUG RAM called the Register Map. In the Register Map, the register contents may be examined or modified using the M command and a predefined mnemonic (or absolute address) of the storage location for that register (example: PC,:A, . . .,:SP). The Register Map is also used to initialize the CPU registers whenever execution is initiated or resumed. Thus the E and B commands can be used together to initiatize, execute, and examine the results of individual program segments.

The B command gives the user the option of having all CPU registers displayed when the breakpoint is encountered. This is done by entering a second operand to the B command. Otherwise DDT-80 defaults to displaying the PC and AF registers. When all CPU registers are displayed, the format is the same as for the R command previously discussed.

#### LOAD, DUMP, AND COPY (L, D, C)

The L and D commands load and dump object files through the object I/O channel in standard Intel Hex format. Checksums are used for error detection, and the addresses of questionable blocks are typed automatically while loading.

The C command will copy the contents of the memory block specified to another block of memory. There are no restrictions on the direction of the copy or on whether the blocks overlap.

#### **HEXADECIMAL ARITHMETIC (H)**

The H command is a dummy command used to allow hexadecimal addition and subtraction for expression evaluation without performing any other operation.

#### **DDT-80 I/O CAPABILITIES**

DDT-80 specifies I/O channels, designated 'Console', 'Object', and 'Source', to which any suitable devices may be assigned. The Channel Assignment Table is located in MDX RAM where is may be examined or modified using the M command. The table addresses correspond to the I/O channels and the table contents correspond to the addresses of the peripheral driver routines. A channel which has a device assignment may have that device assignment changed using the M command. This is accomplished by merely modifying the table contents of that channel's table address to correspond to the new peripheral driver routine. A set of peripheral driver routines is supplied and listed below. This scheme also allows the user to write a driver routine for his own peripheral, load it into memory, and easily configure that peripheral into the system.

#### **DDT-80 1/0 PERIPHERAL DRIVERS**

- 1. A serial input driver (usually a keyboard).

- A serial output driver (usually a CRT or teletype typehead).

- A serial input driver which sends out a reader step signal (usually a teletype reader).

- 4. A serial output driver which forces a delay after a carriage return (usually a Silent 700 typehead).

- A parallel input driver (usually for high speed paper tape output).

- A parallel output driver (usually for high speed paper tape output).

- 7. A parallel output driver (usually for a line printer).

#### **TEXT EDITOR DESCRIPTION**

The Text Editor permits random access editing of ASCII character strings. It can be used as a line or character oriented editor. Individual characters may be located by

position or context. The Editor works on blocks of characters which are typically read into memory from magnetic tape or paper tape. Each edited block can be output to magnetic tape or paper tape after editing is completed. While the primary application for the Text Editor is in editing assembly language source statements, it may be applied to any ASCII text delimited by "carriage returns".

The Editor has a macro command processing option. Up to two sets of commands may be stored and processed at any time during the editing process.

All I/O is done via the DDT-80 channels. The Editor can be used with the MOSTEK ASMB-80 Assembler and Loader to edit, assemble, and load programs in memory without the need for external media for intermediate storage.

The following commands are recognized by the Text Editor:

An - Advance record pointer n records

Bn - Backup record pointer n records

Cn dS1dS2d - Change string S1 to string S2 for n occurrences

Dn - Delete next n records

E - Exchange current record with records to

be inserted

I - Insert records

Ln - Go to line number n

Mn - Enter command buffers (pseudo-macro)

N - Print top, bottom, and current line number

Pn - Punch n records from buffer

R - Read source records into buffer

Sn dS1d - Search for nth occurrence of string S1

#### ASSEMBLER DESCRIPTION

The Assembler reads Z80 source mnemonics and pseudoops and outputs an assembly listing and object code. The assembly listing shows address, machine code, statement number, and source statement. The object code is in industry standard hexadecimal format modified for relocatable, linkable assemblies.

The Assembler supports conditional assemblies, global symbols, relocatable programs, and a printed symbol table. It can assemble any length program, limited only by a symbol table size which is user selectable. Expressions involving addition and subtraction are allowed. A global symbol is categorized as "internal" if it appears as a label in the program; otherwise it is an "external" symbol. The printed symbol table shows which symbols are internal and which are external. The Assembler allows the user to select relocatable or non-relocatable assembly via the "PSECT" pseudo-op. Relocation records are placed in the object output for relocatable assemblies (the MOSTEK

object format is defined below). The Assembler can be run as a single pass assembler or as a learning tool. (In this mode, global symbols and forward references are not allowed).

The following pseudo-ops are recognized by the Assembler:

ORG program origin EQU equate label DEFL define label DEFM define message DEFB define byte DEFW define word DEFS define storage END end statement

NAME - program name definition PSECT - program section definition

GLOBAL - global symbol definition supports the fol-

lowing assembler pseudo-ops

EJECT - eject a page of listing

TITLE - place heading at top of each page

LIST - turn listing on NLIST - turn listing off

#### RELOCATING LINKING LOADER DESCRIPTION

The MOSTEK Relocating Linking Loader provides state-of-the-art capability for loading programs into memory by allowing loading and linking of any number of relocatable and non-relocatable object modules. Non-relocatable modules are always loaded at their starting address as defined by the ORG psuedo-op during assembly. Relocatable object modules can be positioned anywhere in memory at an offset address.

The Loader automatically links and relocates global symbols which are used to provide communication or linkage between program modules. As object programs are loaded, a table containing global symbol references and definitions is built up. At the end of each module, the loader resolves all references to global symbols which are defined by the current or a previously loaded module. It also prints on the console device the number of defined global symbols that have been referenced. The symbol table can be printed to list all global symbols and their load address. The number of object modules which can be loaded by the Loader is limited only by the amount of MDX-RAM available for the modules and the symbol table. Space for the symbol table is allocated dynamically downward in memory from either the top of memory or from a specified address entered as an operand of the load command.

All I/O is done via the DDT-80 channels. Assemblies can be done from source statements stored in memory (by the Editor). The object output can be directed to a memory buffer rather than to an external device. Thus, assembly and loading can be done without external storage media.

The Loader prints the beginning and ending address of each module as it is loaded. The transfer address as defined by the END pseudo-ops is printed for the first module loaded. The Loader execute command (E) can be used to automatically start execution at the transfer address.

The Loader Commands are the following:

L offset - load object module at address "off-set"

plus program origin address

E - execute loaded program at transfer address

of first module

T - print global symbol table

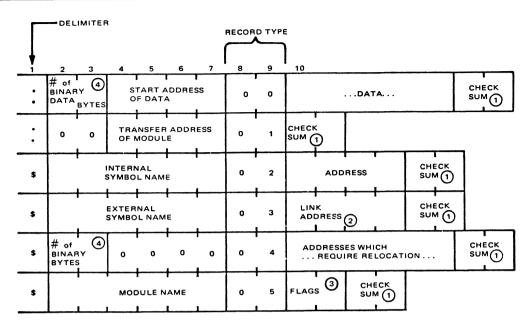

#### MOSTEK OBJECT OUTPUT DEFINITION

Each record of an object module begins with a delimiter (colon or dollar sign) and ends with carriage return and line feed. A colon (:) is used for data records and the end-of-file record. A dollar sign (\$) is used for records containing relocation information and linking information. All information is in ASCII. Each record is identified by "type". The type is determined by the 8th and 9th bytes of the record which can take the following values:

00 - data

01 - end-of-file

02 - internal symbol

03 - external symbol

04 - relocation information

05 - module definition

#### I/O TRANSFER RATE

| X16 Baud Rate Clock | Baud Rate (Hz) |

|---------------------|----------------|

| 1,760               | 110            |

| 4,800               | 300            |

| 9,600               | 600            |

| 19,200              | 1,200          |

| 38,400              | 2,400          |

| 76,800              | 4,800          |

| 153,600             | 9,600          |

| 307,200             | 19,200         |

#### SERIAL COMMUNICATIONS CHARACTERISTICS

Asynchronous

Full duplex operation Start bit verification

Data word size variable from 5 to 8 bits

One or two stop bits

Odd, even, or no parity

One word buffering on both transmit and on receive.

#### NOTES:

- Check Sum is negative of the binary sum of all bytes except delimiter and carriage return/line feed.

- Link Address points to last address in the data which uses the external symbol. This starts a backward link list through the data records 2. for that external symbol. The list terminates at OFFFFH.

- The flags are one binary byte. Bit 0 is defined as: 3.

- 0 absolute module

- 1 relocatable module Maximum of 64 ASCII bytes.

#### SERIAL COMMUNICATIONS INTERFACE

| SIGNAL                    | BUFFERED<br>20mA Curre<br>RS-232 | . •    |

|---------------------------|----------------------------------|--------|

| Transmitted data          | Output                           | Output |

| Received data             | Input                            | Input  |

| Data Terminal Ready (DTR) |                                  | Input  |

| Request to Send (RTS)     |                                  | Input  |

| Carrier Detect (CDET)     |                                  | Output |

| Clear to Send (CTS)       |                                  | Output |

| Data Set Ready (DSR)      |                                  | Output |

| Reader Step relay (RS)    | Output<br>(20mA)                 |        |

#### PARALLEL BUS INTERFACE-STD BUS **COMPATIBLE**

One 74 LS load Max Inputs **Bus Outputs**  $I_{OH} = -3mA$  min at 2.4 Volts

IOI = 12mA min at 0.4 Volts

#### I/O ADDRESSING

On-board Serial I/O Port Control Port DDH DCH Data Port

Module and Reader Step Control Port DEH

#### SYSTEM CLOCK

2.5MHz MDX-DEBUG 1.25MHz MDX-DEBUG-4 1.25MHz 4.0MHz

#### POWER SUPPLY REQUIREMENT

+12 Volts  $\pm5\%$  at 50mA max. - 12 Volts  $\pm$ 5% at 35mA max. +5 Volts +5% at 1.2mA max.

# **Z80 Single Step Module (MDX-SST)**

#### **FEATURES**

- ☐ Hardware single-step capability

- ☐ Compatible with DDT-80 Operating System

- ☐ STD-Z80 BUS compatible

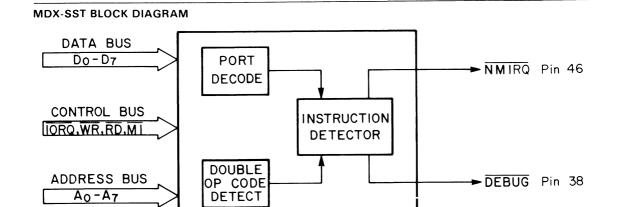

#### **MDX-SST DESCRIPTION**

The MOSTEK MDX-SST was designed to enhance the hardware and software debug capability for MD Series systems. The use of the MDX-SST with the MDX-CPU1 and MDX-DEBUG boards allows the user to single-step instructions through RAM and/or EPROM/ROM with the capability of displaying all of the MDX-CPU1 registers on each instruction execution.

The MDX-SST board is implemented using the MDX-CPU1's nonmaskable interrupt and is controlled by firmware from the keyboard. When the command to single step an instruction is given, the sequence of events is the same as executing a program except that a "1" is output to the single step control port (DFH) instead of a "0". The circuit decodes the double M1 instructions (CBH, DDH, EDH, or FDH) and M1 is used to clock a shift register circuit which (if a "1" is output to port DFH) generates a nonmaskable interrupt at the start of the instruction to be single stepped. The nonmaskable interrupt saves the address of execution on the stack and causes the next instruction to be fetched from address E066H. The shift register is clocked twice after the nonmaskable interrupt, causing the signal DEBUG to go low, forcing "E" on the most significant address lines, and causing the instruction to be fetched from the E066H in the operating system DDT-80. The operating system then jumps to EO69H. clears the debug flip-flop by reading PORT DFH, saves the MDX-CPU1 registers in the MDX-CPU1 scratch RAM, and waits for the next command.

The single-step command is implemented in DDT-80 which resides on the MDX-DEBUG board and has the following format:

#### S COMMAND, Single-step

This command allows the user to start single-stepping from a given location for a given number of instructions and to display the CPU registers after each step.

Format:

.S aaaa (cr)

.S (cr)

.S aaaa,nn,b(cr) start single-stepping at location aaaa

for nn steps or instructions. If b=0, display only the PC and AF registers, if  $b\neq 0$ , display all the CPU registers. the same as above with b=0

.S aaaa,nn (cr) the same assumed.

and the MDX-DEBUG.

the same as above with nn=1 and b=0 assumed.

the same as above with nn=1 and b=0 assumed; aaaa is set equal to the

contents of the user's PC.

The use of the MDX-SST board requires the MDX-CPU1

SYSTEM CLOCK

MIN 500KHz MAX 4.00MHz

PARALLEL BUS INTERFACE STD-Z80 BUS COMPATIBLE

POWER SUPPLY REQUIREMENTS

+5Vdc @ 85mA

**OPERATING TEMPERATURE**

0°C to 50°C

#### **ELECTRICAL SPECIFICATIONS**

PORT ADDRESS (HEX)

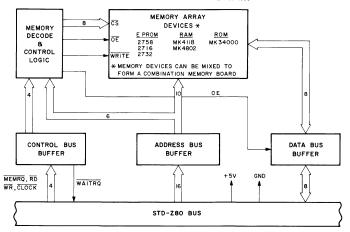

# **Universal Memory Card (MDX-UMC)**

#### **FEATURES**

□ Can be strapped to accept the following industrystandard memory devices:

| EPROM         | STATIC RAM      | ROM              |

|---------------|-----------------|------------------|

| 2758 (1K x 8) | MK4118 (1K x 8) |                  |

| 2716 (2K x 8) | MK4802 (2K x 8) | MK34000 (2K x 8) |

| 2732 (4K x 8) |                 |                  |

- □ Memories can be mixed to form a combination memory board

- ☐ Wait state generator for 4MHz operation

- □ STD-Z80 BUS compatible

- □ +5 Volt only

#### MDX-UMC DESCRIPTION

The MDX-UMC is one of MOSTEK's complete line of STD-Z80 BUS compatible microcomputer modules.

Designed as a universal memory card for the STD-Z80 BUS, the MDX-UMC provides the user with the capability of configuring the board to meet the system requirement of ROM/EPROM and/or RAM. By the use

#### **ELECTRICAL SPECIFICATIONS**

#### **WORD SIZE**

8 bits

#### **MEMORY ADDRESSING**

4K boundaries

#### MEMORY CAPACITY

8 sockets

Sockets are strapped in pairs to accomodate the following memories:

| <b>EPROM</b> | STATIC RAM | ROM     |

|--------------|------------|---------|

| 2758         | MK4118     |         |

| 2716         | MK4802     | MK34000 |

| 2732         |            |         |

#### 2732

### PARALLEL BUS INTERFACE - STD-Z80 BUS COMPATIBLE

Inputs: One 74LS load max.

BUS Outputs:  $I_{OH} = -15mA$  min at 2.4 Volts

$I_{\rm OL}$  = 24mA min at 0.5 Volts

of strapping options, the user is able to configure pairs of sockets for ROM/EPROM/RAM to form a combination memory board.

Other MDX-UMC features include 4K boundary addressing and an optional wait-state generator to accommodate slower memories for 4MHz operations.

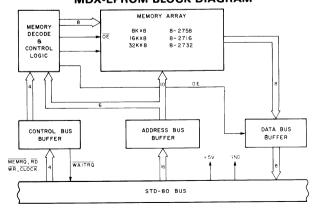

#### MDX-UMC BLOCK DIAGRAM

# **EPROM Module (MDX-EPROM)**

#### **FEATURES**

☐ Accepts the following industry standard EPROMS: 2758 (1K x 8)

2716 (2K x 8)

2732 (4K x 8)

☐ Eight EPROM sockets for maximum storage of:

8K x 8 using 2758's

16K x 8 using 2716's

32K x 8 using 2732's

□ Wait state generator for 4MHz operation

□ STD-Z80 BUS compatible

□ +5 Volt only

#### MDX-EPROM DESCRIPTION

The MDX-EPROM is designed to be an EPROM memory expansion board for the MOSTEK MD SERIES™ of Z80based microcomputers. The MDX-EPROM accepts the following EPROMS; 2758 (1K x 8), 2716 (2K x 8) and 2732 (4K x 8) which gives a maximum storage capacity of 8K, 16K, or 32K bytes respectively.

Starting address selection is provided for positioning the MDX-EPROM on any 4K boundary. A wait-state generator is also provided for optional 4MHz operation.

#### **ELECTRICAL SPECIFICATIONS**

#### **WORD SIZE**

8 bits

#### **MEMORY CAPACITY**

8K x 8 using eight 2758's

16K x 8 using eight 2716's\*

32K x 8 using eight 2732's

\*EPROMS included

#### REQUIRED ACCESS TIME

| MEMORY<br>TIME      | MIN ACCESS<br>TIME | CYCLE TIME |

|---------------------|--------------------|------------|

| 2758, 2716,<br>2732 | 450ns*             | 450ns      |

<sup>\*</sup>One wait state must be added for 4MHz operation.

#### ADDRESS SELECTION

4K boundaries

#### **BUS INTERFACE**

STD-Z80 BUS compatible

One 74LS load max. Inputs: **Bus Outputs:**

$I_{OH} = -15$ mA min at 2.4 Volts

IOH = 24mA min at 0.5 Volts

#### **POWER SUPPLY REQUIREMENTS\***

+5 Volts ± 5% at 0.45A

\*Does not include EPROMs. Add 100 mA for each EPROM.

#### MDX-EPROM BLOCK DIAGRAM

## Static RAM Module (MDX-SRAM)

#### **FEATURES**

□ Three memory sizes

4K x 8 (MDX-SRAM4)

8K x 8 (MDX-SRAM8)

16K x 8 (MDX-SRAM16)

☐ Selectable starting adddress on 4K boundaries

□ 2.5 MHz and 4.0 MHz compatible

□ STD-Z80 BUS compatible

□ +5 Volt only

#### MDX-SRAM DESCRIPTION

The MDX-SRAM is designed to be a static RAM Memory expansion board for the MOSTEK MD SERIES of Z80 based microcomputers. It is available in three memory capacities; 4K bytes (MDX-SRAM4), 8K bytes (MDX-SRAM8), and 16K bytes (MDX-SRAM16). Additionally, all MDX-SRAM boards are 2.5MHz and 4.0MHz compatible. Thus, the designer can choose from three options available and tailor the add-on static RAM directly to the system requirements.

The MDX-SRAM is designed using the state of the art MK4118 (1Kx8) static RAM and MK4802 (2Kx8) static

RAM memory devices. Because of the high speed of the MK4118 and MK4802, no wait states are necessary for operating the MDX-SRAM at 2.5MHz or 4.0MHz. Address selection is provided on all MDX-SRAM cards for positioning the 4K, 8K, or 16K of memory to start on any 4K boundary.

#### ADDRESS SELECTION

Selection of 4K, 8K, or 16K contiguous memory blocks to begin on any 4K boundary.

#### **BUS INTERFACE**

STD-Z80 BUS compatible

Inputs: One 74LS load max

Bus Outputs:  $I_{OH} = -15$ mA min at 2.4 Volts

$I_{\rm OL}$  = 24mA min at 0.5 Volts

#### **POWER SUPPLY REQUIREMENTS**

| BOARDS     | +5V ± 5%  |

|------------|-----------|

| MDX-SRAM4  | 0.8 A max |

| MDX-SRAM8  | 1.2 A max |

| MDX-SRAM16 | 1.2 A max |

#### **ELECTRICAL SPECIFICATIONS**

#### **WORD SIZE**

8 bits

#### MEMORY SIZE

MDX-SRAM4 - 4,096 bytes MDX-SRAM8 - 8,192 bytes MDX-SRAM16 - 16,384 bytes

#### **TIMING**

|          | MEMORY<br>ACCESS | MEMORY<br>CYCLE |

|----------|------------------|-----------------|

| MDX-SRAM | 250ns max.       | 250ns min.      |

#### MDX-SRAM BLOCK DIAGRAM

# Analog to Digital Conversion Module (MDX-A/D)

## **FEATURES**

- 8-Bit A/D converter with 16 single-ended analog inputs

- □ 3 full-scale input ranges

- 0 to +1 Volts

- 0 to +2 Volts

- 0 to +5 Volts

- □ Total unadjusted error < ± ½ LSB

- □ Linearity error < ± ½ LSB

- □ No missing codes

- ☐ Guaranteed monotonicity

- □ No zero adjust required

- □ No full scale adjust required

- Provisions for additional channel expansion

- □ Optional sample and hold

- □ Address programmable

- □ 4MHz option

- □ Compatible with STD-Z80 BUS

## DESCRIPTION

The MD Series and the STD-Z80 BUS were designed to satisfy the need for low-cost OEM microcomputer modules. The STD-Z80 BUS uses a motherboard interconnect system concept and is designed to handle any MD Series card type in any slot. The modules for the STD-Z80 BUS are a compact 4.5 x 6.5 inches which provides for system partitioning by function (RAM, EPROM, I/O). This smaller module size makes system packaging easier while increasing MOS-LSI densities providing high functionality per module.

The MD Series of OEM microcomputer boards and the STD-Z80 BUS offer the most cost effective system configuration available to the OEM system designer.

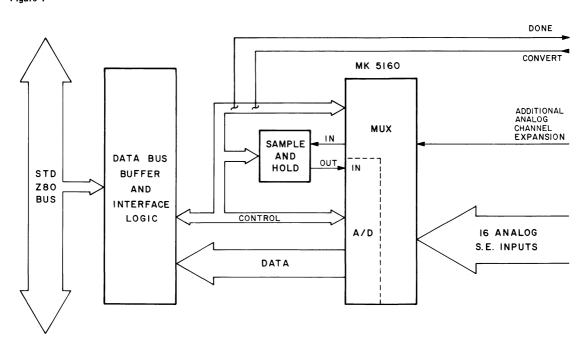

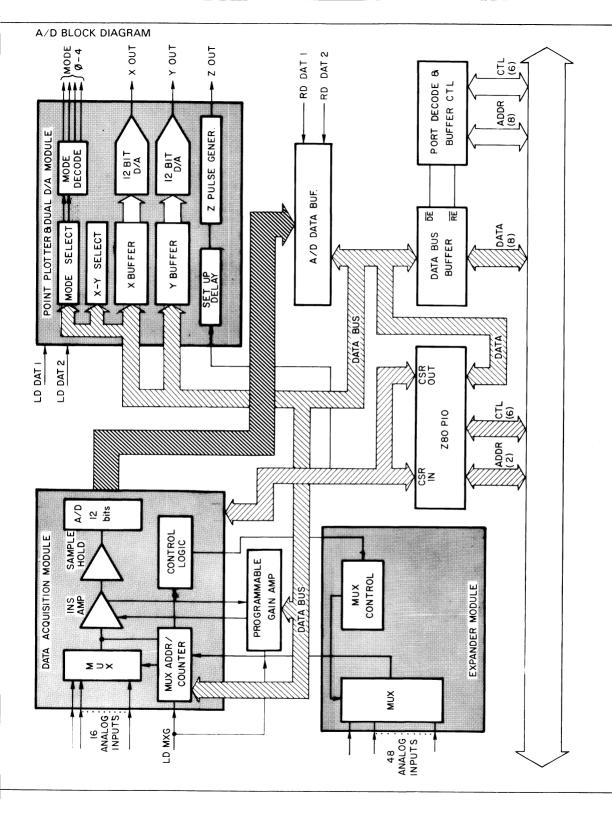

### MDX-A/D DESCRIPTION

The Analog to Digital Converter Module, MDX-A/D, is designed to be a 16 channel single-ended A/D module

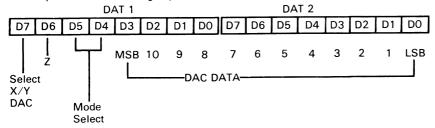

for the STD-Z80 BUS. The module is designed around the MOSTEK MK5160 8-bit A/D converter/16 channel analog multiplexer. Additional provisions have been included to allow further analog expansion if desired. Also, an optional Sample and Hold module (AD582) may be added to increase system performance. Figure 1 is a block diagram of the MDX-A/D showing the major elements of the module.

The first element of this board is the multiplexer. This 16-channel multiplexer can directly access any one of 16 single-ended analog channels and provides logic for additional channel expansion. All analog input lines contain a diode/resistor protection circuit to reduce damage potential from overvoltage and transient inputs.

The output of the multiplexer can either drive the A/D converter directly or a Sample and Hold (S/H) module version is available. The board is shipped normally without a Sample and Hold.

If an S/H function is required, an Analog Devices AD582 needs to be inserted and one jumper removed. This circuitry allow sampling of signals up to 5KHz with a nominal 150nsec aperture time.

The other half of the MK5160 is the A/D converter. The 8-bit A/D consists of 256 series resistors with an analog switch tree, a chopper stabilized comparator and a sucessive approximation register. The series resistor approach guarantees monotonicity and no missing codes. The need for external zero and full-scale adjustments has been eliminated and an absolute accuracy of  $\leqslant 1\,$  LSB including quantizing error is provided. A start convert signal initiates the conversion process and can be jumper selected from either an external source or under program control. Upon completion, a DONE signal is generated to indicate end of conversion. This signal is used to flag the program as well as any external device.

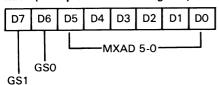

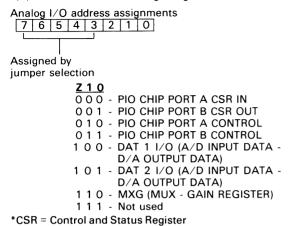

The Data Bus Buffer and Interface Logic allows the MDX-A/D module to interface with the STD-Z80 BUS. It provides buffering for all signals as well as address decoding and A/D port control. A total of 4 port address locations are required and can start on any four-word boundary.

## **ELECTRICAL SPECIFICATIONS**

## **WORD SIZE**

Data: 8 bits

I/O Addressing: 8 bits

## I/O ADDRESSING

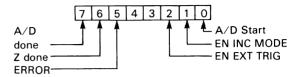

On board programmable on 4-word boundaries X X X X X X O O A/D Port Configuration Data X X X X X X O 1 A/D Port Configuration Control X X X X X X 1 O A/D Data Input/Output Port X X X X X X 1 1 Data Control Port

#### I/O CAPACITY

Eight bit analog to digital converter with up to sixteen single ended analog input channels. Channel expansion available. Start conversion and done handshake signals available at the edge connector.

Three full scale input ranges: 0 to +I Volt, 0 to +2 Volts and 0 to +5 Volts.

#### **INTERRUPTS**

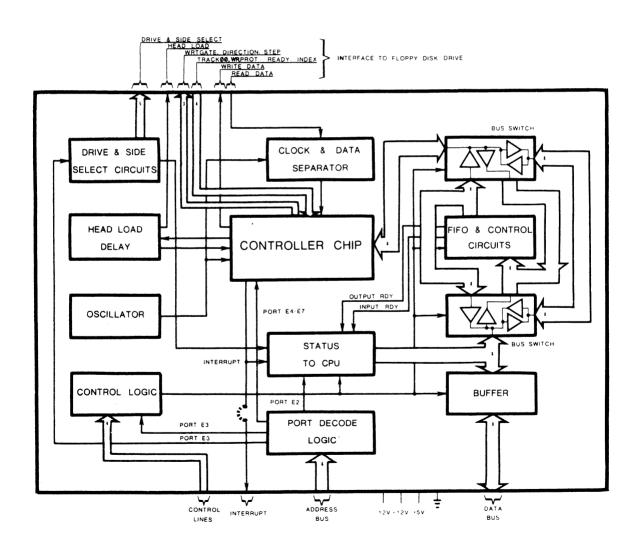

Vectored interrupts generated. Interrupt vector programmable upon initialization. Daisy-chained interrupt priority. Interrupts are controlled by a MOSTEK MK3881 Parallel I/O controller chip.